DOCUMENT: ZX200-AC2-N1080A

SUBJECT: ZX200 Vs Agilent N1080A

# Comparison test case study using Zebax ZX200 vs. Agilent N1080A HDMI test fixture ( aka. Test board )

The subsequent pages are full test record using Agilent N1080A HDMI test fixture

Test Case: **4Kx2K 30 Hz PRN** HDMI Clock Frequency: **2.96GHz**

Full comparison chart can be found here:

ZX200-vs-Agilent-4Kx2K-ZXTR-ZX200-AC2-N1080A.pdf

# **HDMI Test Report**

Overall Results:0 of 20 Tests Failed

| Test Configuration Details |                                           |  |  |  |

|----------------------------|-------------------------------------------|--|--|--|

| Device Description         |                                           |  |  |  |

| Device Name                | Quantum 804A                              |  |  |  |

| Comments                   | Agilent Fixture 4K X2K 30 Hz PRN output 1 |  |  |  |

| Device ID                  | Transmitter                               |  |  |  |

| ConnectionType             | ype 4 Connections                         |  |  |  |

| HDMI Specification         | 1.4                                       |  |  |  |

| Test Fixture Type          | N1080A                                    |  |  |  |

| Test Session Details       |                                           |  |  |  |

| Infiniium SW Version       | 05.71.0000                                |  |  |  |

| Infiniium Model Number     | DSO81204B                                 |  |  |  |

| Infiniium Serial Number    | MY46002010                                |  |  |  |

| Application SW Version     | 1.03.9002                                 |  |  |  |

| Last Test Date             | 4/1/2013 10:59:52 AM                      |  |  |  |

# **Summary of Results**

| Margin Thresholds |       |  |  |  |

|-------------------|-------|--|--|--|

| Warning           | < 2 % |  |  |  |

| Critical          | < 0 % |  |  |  |

| Pass | # Failed | # Trials | Test Name                      | Actual Value | Margin  | Spec Range                         |

|------|----------|----------|--------------------------------|--------------|---------|------------------------------------|

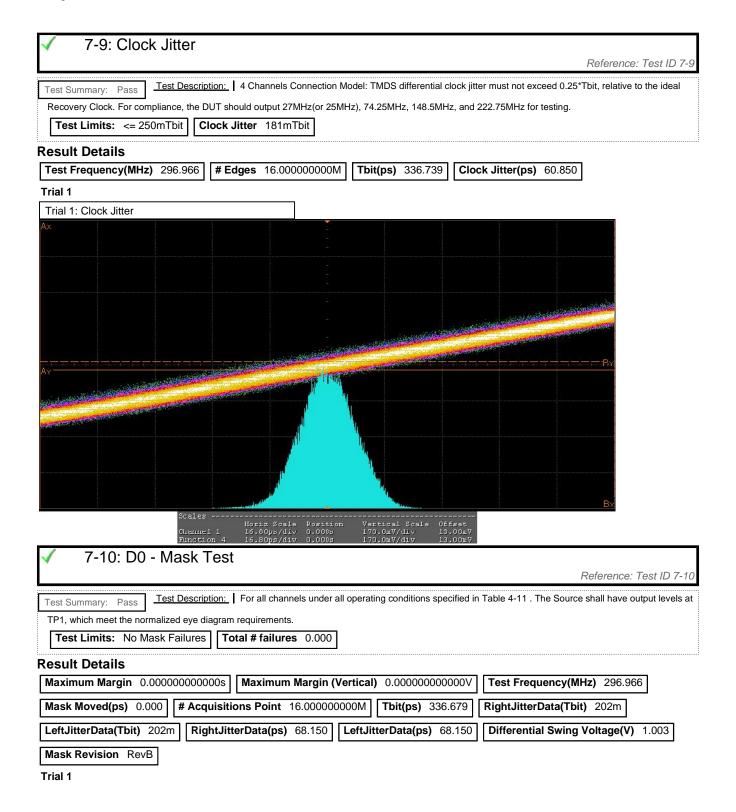

| 1    | 0        | 1        | 7-9: Clock Jitter              | 181mTbit     | 27.6 %  | VALUE <= 250mTbit                  |

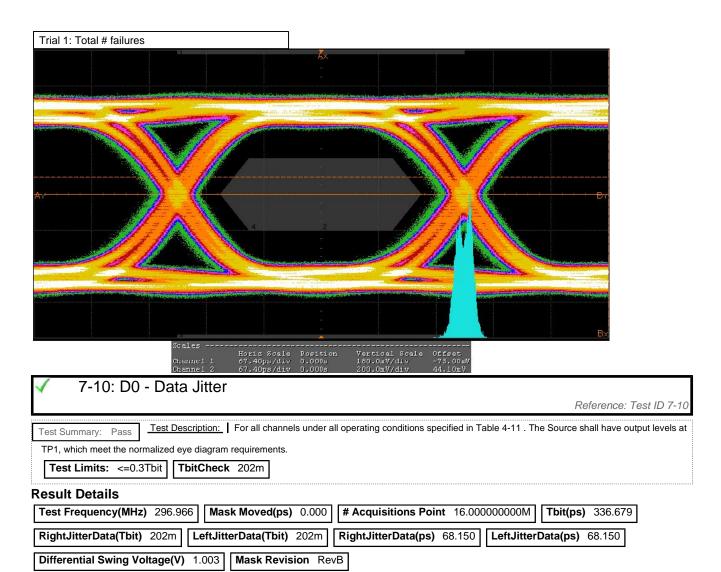

| 1    | 0        | 1        | 7-10: D0 - Mask Test           | 0.000        | 50.0 %  | No Mask Failures                   |

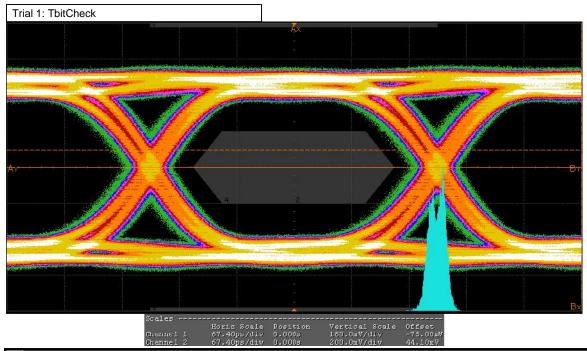

| 1    | 0        | 1        | <u>7-10: D0 - Data Jitter</u>  | 202m         | 32.7 %  | <=0.3Tbit                          |

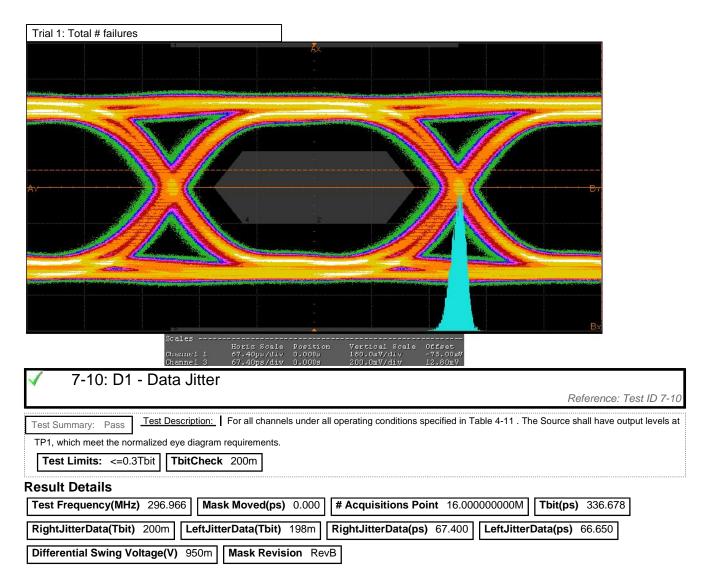

| 1    | 0        | 1        | 7-10: D1 - Mask Test           | 0.000        | 50.0 %  | No Mask Failures                   |

| 1    | 0        | 1        | <u>7-10: D1 - Data Jitter</u>  | 200m         | 33.3 %  | <=0.3Tbit                          |

| 1    | 0        | 1        | 7-10: D2 - Mask Test           | 0.000        | 50.0 %  | No Mask Failures                   |

| 1    | 0        | 1        | <u>7-10: D2 - Data Jitter</u>  | 189m         | 37.0 %  | <=0.3Tbit                          |

| 1    | 0        | 1        | 7-4: Clock Rise Time           | 203.250ps    | 171.0 % | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | 7-4: Clock Fall Time           | 186.530ps    | 148.7 % | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | 7-4: D0 - Rise Time            | 94.840ps     | 26.5 %  | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | 7-4: D0 - Fall Time            | 93.580ps     | 24.8 %  | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | 7-4: D1 - Rise Time            | 92.690ps     | 23.6 %  | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | 7-4: D1 - Fall Time            | 90.320ps     | 20.4 %  | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | <u>7-4: D2 - Rise Time</u>     | 99.130ps     | 32.2 %  | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | 7-4: D2 - Fall Time            | 93.070ps     | 24.1 %  | VALUE >= 75.000ps                  |

| 1    | 0        | 1        | 7-8: Clock Duty Cycle(Minimum) | 49.420       | 23.6 %  | >=40%                              |

| 1    | 0        | 1        | 7-8: Clock Duty Cycle(Maximum) | 50.350       | 16.1 %  | <=60%                              |

| 1    | 0        | 1        | 7-6: Inter-Pair Skew - D0/D1   | 4mTpixel     | 49.0 %  | -200mTpixel <= VALUE <= 200mTpixel |

| 1    | 0        | 1        | 7-6: Inter-Pair Skew - D0/D2   | 4mTpixel     | 49.0 %  | -200mTpixel <= VALUE <= 200mTpixel |

| 1    | 0        | 1        | 7-6: Inter-Pair Skew - D1/D2   | 2mTpixel     | 49.5 %  | -200mTpixel <= VALUE <= 200mTpixel |

# **Report Detail**

## 7-10: D1 - Mask Test

Reference: Test ID 7-10

Test Summary: Pass Test Description: For all channels under all operating conditions specified in Table 4-11 . The Source shall have output levels at TP1, which meet the normalized eye diagram requirements.

Test Limits: No Mask Failures | Total # failures 0.000

#### **Result Details**

Maximum Margin0.0000000000000Maximum Margin (Vertical)0.0000000000000Test Frequency(MHz)296.966Mask Moved(ps)0.000# Acquisitions Point16.000000000MTbit(ps)336.678RightJitterData(Tbit)200mLeftJitterData(Tbit)198mRightJitterData(ps)67.400LeftJitterData(ps)66.650Differential Swing Voltage(V)950m

Mask Revision RevB

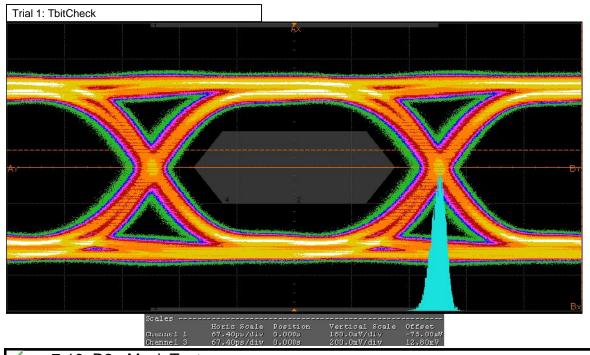

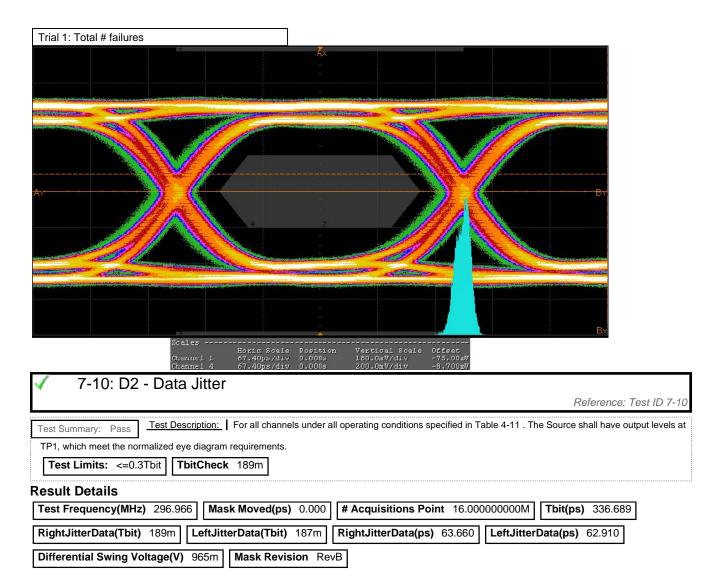

## 7-10: D2 - Mask Test

Reference: Test ID 7-10

Test Summary: Pass Test Description: For all channels under all operating conditions specified in Table 4-11 . The Source shall have output levels at TP1, which meet the normalized eye diagram requirements.

Test Limits: No Mask Failures | Total # failures 0.000

#### **Result Details**

Maximum Margin0.0000000000000Maximum Margin (Vertical)0.0000000000000Test Frequency(MHz)296.966Mask Moved(ps)0.000# Acquisitions Point16.000000000MTbit(ps)336.689RightJitterData(Tbit)189mLeftJitterData(Tbit)187mRightJitterData(ps)63.660LeftJitterData(ps)62.910Differential Swing Voltage(V)965m

Mask Revision RevB

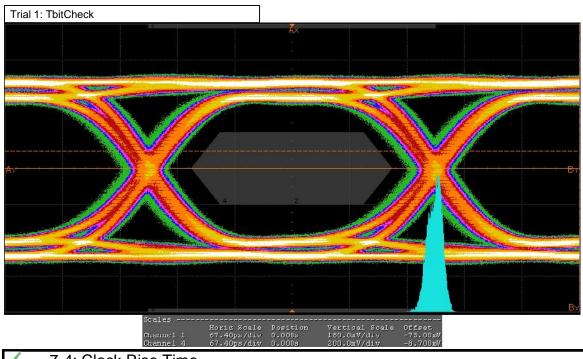

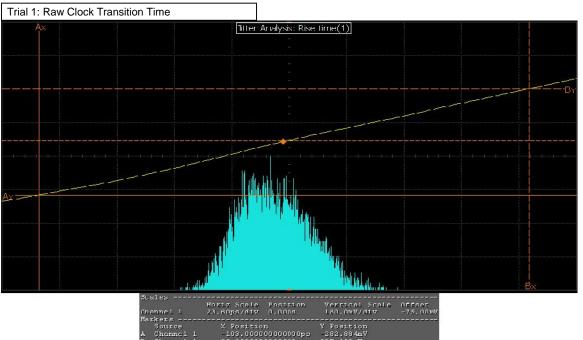

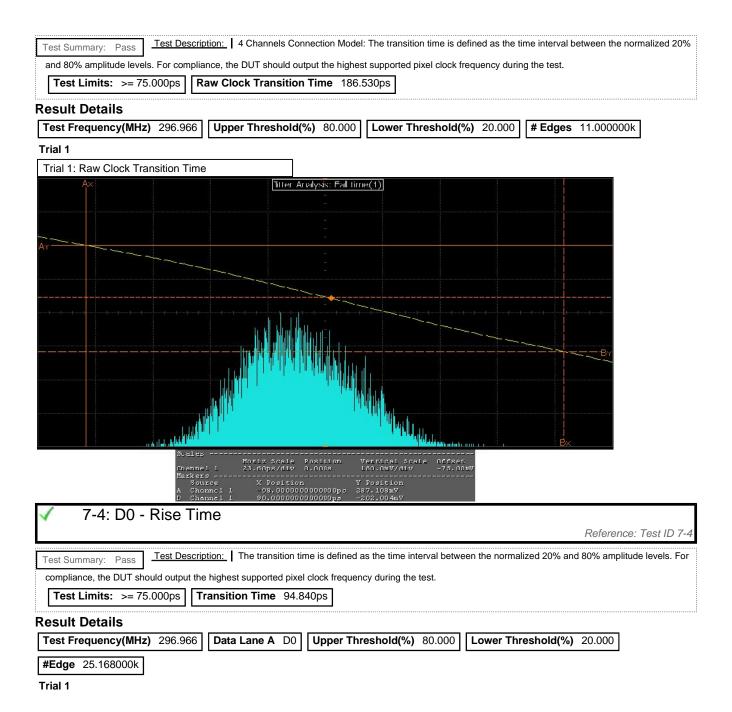

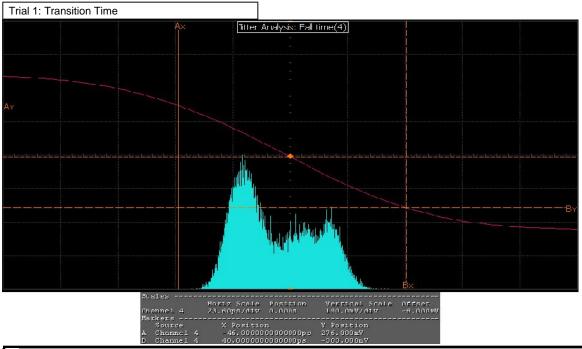

# 7-4: Clock Rise Time

Reference: Test ID 7-4

Test Summary: Pass Test Description: 4 Channels Connection Model: The transition time is defined as the time interval between the normalized 20% and 80% amplitude levels. For compliance, the DUT should output the highest supported pixel clock frequency during the test.

Test Limits: >= 75.000ps Raw Clock Transition Time 203.250ps

#### **Result Details**

Test Frequency(MHz) 296.966 Upper Threshold(%) 80.000 Lower Threshold(%) 20.000 # Edges 11.000000k

## Trial 1

7-4: Clock Fall Time

Reference: Test ID 7-4

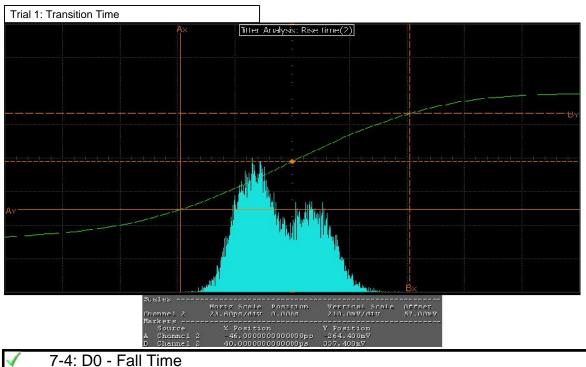

√ 7-4: D0 - Fall Time

Reference: Test ID 7-4

Re

Test Summary: Pass Test Description: The transition time is defined as the time interval between the normalized 20% and 80% amplitude levels. For compliance, the DUT should output the highest supported pixel clock frequency during the test.

Test Limits: >= 75.000ps Transition Time 93.580ps

#### **Result Details**

Test Frequency(MHz) 296.966 Data Lane A D0 Upper Threshold(%) 80.000 Lower Threshold(%) 20.000

#Edge 25.873000k

#### Trial 1

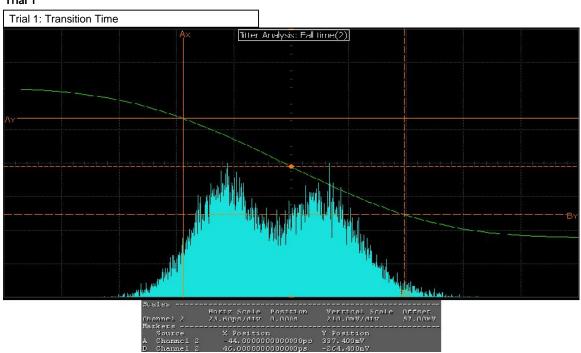

7-4: D1 - Rise Time

Reference: Test ID 7-Test Description: The transition time is defined as the time interval between the normalized 20% and 80% amplitude levels. For Pass Test Summary: compliance, the DUT should output the highest supported pixel clock frequency during the test. **Test Limits:** >= 75.000ps Transition Time 92.690ps **Result Details** Test Frequency(MHz) 296.966 Data Lane A D0 Upper Threshold(%) 80.000 Lower Threshold(%) 20.000 #Edge 25.852000k Trial 1 Trial 1: Transition Time Titter Analysis: Rise time(3) Horiz Scale 23.60ps/div Vertical Scal 190.0mV/div 7-4: D1 - Fall Time Reference: Test ID 7-

Test Description: The transition time is defined as the time interval between the normalized 20% and 80% amplitude levels. For Test Summary: compliance, the DUT should output the highest supported pixel clock frequency during the test.

**Test Limits:** >= 75.000ps Transition Time 90.320ps

#### **Result Details**

Test Frequency(MHz) 296.966 Data Lane A D0 Upper Threshold(%) 80.000 Lower Threshold(%) 20.000

**#Edge** 24.715000k

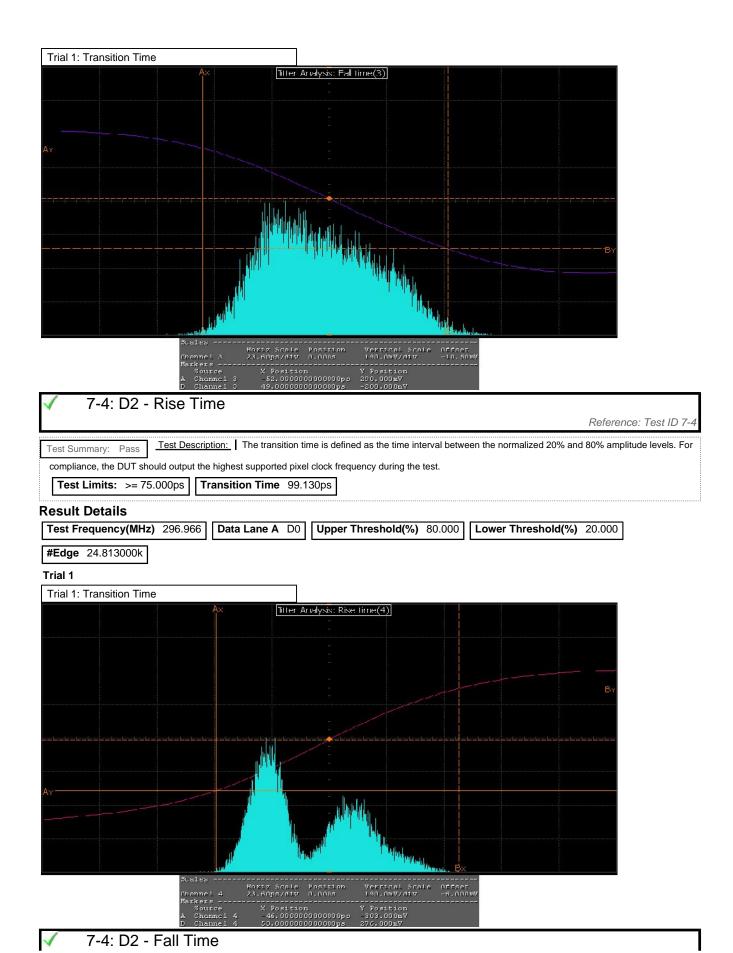

Reference: Test ID 7-4

Test Summary: Pass Test Description: The transition time is defined as the time interval between the normalized 20% and 80% amplitude levels. For

Test Limits: >= 75.000ps Transition Time 93.070ps

compliance, the DUT should output the highest supported pixel clock frequency during the test.

#### **Result Details**

Test Frequency(MHz)296.966Data Lane ADOUpper Threshold(%)80.000Lower Threshold(%)20.000

#Edge 24.787000k

#### Trial 1

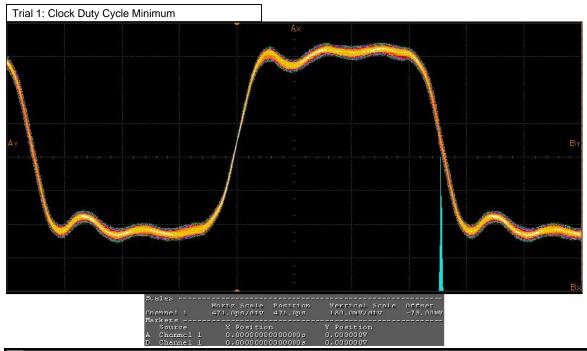

# 7-8: Clock Duty Cycle(Minimum)

Reference: Test ID 7-8

Test Summary: Pass Test Description: 4 Channels Connection Model: Clock duty cycle must be at least 40% and not more than 60%. The Source shall meet the AC specifications in Table 4-13 across all operating conditions specified in Table 4-11. For compliance, the DUT should output the highest

Test Limits: >=40% Clock Duty Cycle Minimum 49.420

supported pixel clock frequency during the test.

#### **Result Details**

Test Frequency(MHz) 296.966 # Edges 10.000000k | TdutyMIN(ns) 1.664

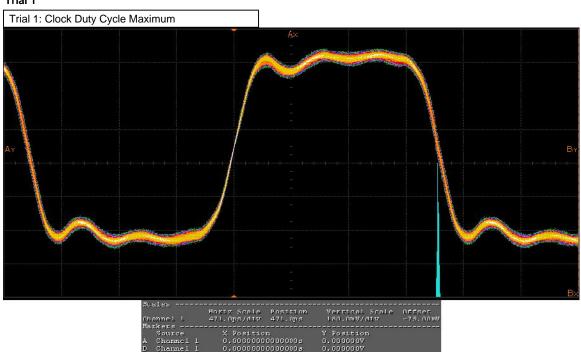

# 7-8: Clock Duty Cycle(Maximum)

Reference: Test ID 7-8

Test Summary: Pass Test Description: 4 Channels Connection Model: Clock duty cycle must be at least 40% and not more than 60%. The Source shall meet the AC specifications in Table 4-13 across all operating conditions specified in Table 4-11. For compliance, the DUT should output the highest

Test Limits: <=60% Clock Duty Cycle Maximum 50.350

supported pixel clock frequency during the test.

#### **Result Details**

Test Frequency(MHz)

296.966

# Edges

10.000000k

TdutyMAX(ns)

1.696

#### Trial 1

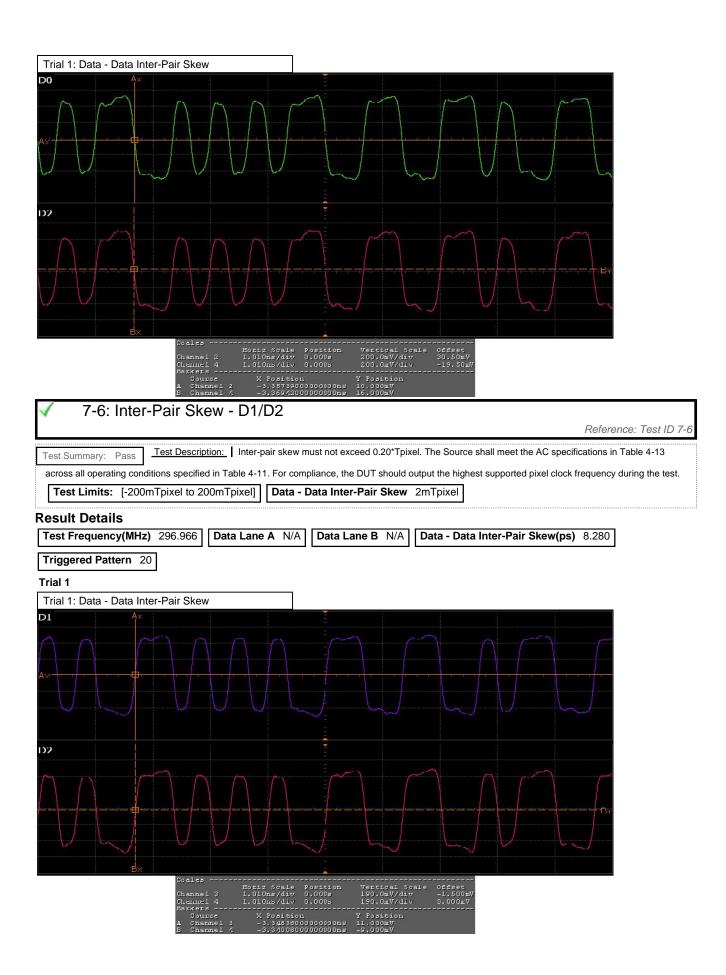

7-6: Inter-Pair Skew - D0/D1

Reference: Test ID 7-6 <u>Test Description:</u> Inter-pair skew must not exceed 0.20\*Tpixel. The Source shall meet the AC specifications in Table 4-13 Test Summary: Pass across all operating conditions specified in Table 4-11. For compliance, the DUT should output the highest supported pixel clock frequency during the test. Test Limits: [-200mTpixel to 200mTpixel] Data - Data Inter-Pair Skew 4mTpixel **Result Details** Test Frequency(MHz) 296.966 Data Lane A N/A Data Lane B N/A Data - Data Inter-Pair Skew(ps) 13.980 Triggered Pattern Trial 1 Trial 1: Data - Data Inter-Pair Skew DO 101 7-6: Inter-Pair Skew - D0/D2 Reference: Test ID 7-0 <u>Test Description:</u> Inter-pair skew must not exceed 0.20\*Tpixel. The Source shall meet the AC specifications in Table 4-13 Test Summary: across all operating conditions specified in Table 4-11. For compliance, the DUT should output the highest supported pixel clock frequency during the test. Test Limits: [-200mTpixel to 200mTpixel] Data - Data Inter-Pair Skew 4mTpixel **Result Details** Test Frequency(MHz) 296.966 Data Lane A N/A Data Lane B N/A Data - Data Inter-Pair Skew(ps) 12.030

Triggered Pattern 20

#### **Notice**

ALL ZEBAX TECHNOLOGIES DESIGN SPECIFICATIONS, DRAWINGS, PUBLICATIONS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." ZEBAX MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE.

Information furnished is believed to be accurate and reliable. However, Zebax Technologies assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. Specifications mentioned in this publication are subject to change without notice. This publication replaces all other information previously supplied. Zebax Technologies products are not authorized as in life support devices or systems.

#### Copyright

© 2011 Zebax Technologies. All rights reserved.